# APPLICATION NOTE Improved Picture Quality

AN97017

Module MK6-V1 V2.0

#### **Abstract**

This document describes the hardware content, the signal processing and the software control of the 100 Hz scan converter module MK6. The module can be implemented into different TV signal processing architectures. This means, it can be adapted to different colour decoder and deflection processor concepts.

The main signal processing features of the module are 100 Hz scan conversion with median filter based line-flicker reduction, progressive scan, vertical zoom, noise reduction and cross colour reduction. These features are provided by the SAA 4990 (PROZONIC). Also a horizontal aspect ratio conversion can be performed, either by the optional IC SAA 4995 (PANIC), or by an appropriate frequency ratio of the memory writing to the reading frequency, if the IC SAA 4995 should not be used.

The memory controller SAA 4952 is applied to generate the necessary clock and control signals for the memories and the signal processing ICs. This module is also equipped with a slave microcontroller which provides an easy to handle external I<sup>2</sup>C user interface and controls internally the above mentioned signal processing ICs via the SNERT-bus interface.

The I<sup>2</sup>C bus user interface is described in detail in this document.

© Philips Electronics N.V. 1997

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

#### **APPLICATION NOTE**

# Improved Picture Qualtiy Module MK6-V1 V2.0

#### AN97017

#### **Authors:**

P. Kelting, N. Lahann, B. Laue Systems Laboratory Hamburg, Germany

#### Keywords

IPQ

ECO4

PANIC

PROZONIC

VEDA

HORIZONTAL ZOOM

VERTICAL ZOOM

LFR

MOVIE PHASE DETECTION

PROGRESSIVE SCAN

Date: 11 December 1997

# Application Note AN97017

#### **Summary**

The IPQ-Module is a scan converter with analog baseband inputs and outputs Y,-(R-Y) and -(B-Y). It supports the following display modes:

- 50/60 Hz to 100/120 Hz conversion with line flicker reduction LFR (AA\*B\*B) or a simple field repetition (AABB)

- Progressive Scan 50 Hz/1250 lines or 60Hz/1050 lines, interlaced

- Frame repetition mode for movie sources

- Multi-PIP support

- Horizontal zoom (10%, 12.5%, 33%, 50% or 100%)

- Horizontal compression linear and nonlinear with 33%

- Advanced still picture (AA\*AA\*)

- Vertical zoom (10%, 12.7%, 33%, 50% or 100%)

Additionally the following main features are supported:

- Digital CTI (colour transient improvement)

- · Luminance peaking function

- · Adaptive noise and cross-colour reduction with different reduction levels

- · Black side panels

- Screen fade

- · Adaptive LFR control for movie sources

6.2.13

| _<br> | mpro                                   | ved Pic                                                                                                        | ture Quality Module MK6-V1 V2.0                                                                                                                                                                                                                                                                                                                                         | Application Note<br>AN97017 |

|-------|----------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| CC    | NTEN                                   | ITS                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                         |                             |

| 1.    | Introd<br>1.1<br>1.2                   | Definition                                                                                                     | s, Acronyms and Abbreviations                                                                                                                                                                                                                                                                                                                                           |                             |

| 2.    | Hardw                                  | are descri                                                                                                     | ption                                                                                                                                                                                                                                                                                                                                                                   |                             |

| 3.    |                                        |                                                                                                                | ne SAA 4990 PROZONIC                                                                                                                                                                                                                                                                                                                                                    |                             |

|       |                                        | •                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                         |                             |

| 4.    | Gener<br>4.1                           |                                                                                                                | e description                                                                                                                                                                                                                                                                                                                                                           |                             |

| 5.    | <b>I<sup>2</sup>C-bu</b><br>5.1<br>5.2 | Definition                                                                                                     | of the interface                                                                                                                                                                                                                                                                                                                                                        |                             |

|       | <ul><li>5.3</li><li>5.4</li></ul>      | Receiving 5.3.1 5.3.2                                                                                          | status information from the IPQ μC                                                                                                                                                                                                                                                                                                                                      |                             |

| 6.    | Funct                                  | ional desc                                                                                                     | ription                                                                                                                                                                                                                                                                                                                                                                 |                             |

|       | 6.1                                    | Field mer<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11 | LFR mode                                                                                                                                                                                                                                                                                                                                                                |                             |

|       | 6.2                                    | 6.1.12                                                                                                         | Vertical Zoom Function  y control commands  General  Frequency selection (only on modules without SAA 4998  PANIC control (only relevant if the SAA 4995 is implemed Acquisition field frequency  Initialization command  Noise reduction  Split screen function.  Screen fade function  µC port control  Prozonic control byte HOR_DELAYS.  HDDEL control  HD control. |                             |

| Ir  | nprov               | ed Pict                                                                                                                        | ture Quality Module MK6-V1 V2.0                                                                                                                                                                                                                                             | Application Note AN97017 |

|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|     |                     | 6.2.14<br>6.2.15<br>6.2.16<br>6.2.17<br>6.2.18<br>6.2.19<br>6.2.20<br>6.2.21<br>6.2.22<br>6.2.23<br>6.2.23<br>6.2.24<br>6.2.25 | MSB control .  HWE1 delay function  VWE1 delay function  Field blanking function  NPIP_4x4 .  SPIP.  P23 (FILL) .  P27 (PLLMID) .  Taste register (LIMERIC, SAA 4945) .  Status register (LIMERIC) .  WVAL, wanted value (LIMERIC) .  NOISE EST. setting register (LIMERIC) |                          |

| 7.  | <b>SNER</b> 7.1 7.2 | SNERT in<br>7.1.1<br>7.1.2                                                                                                     | Illel interface                                                                                                                                                                                                                                                             |                          |

| 8.  | Functi<br>8.1       |                                                                                                                                | I of VEDA (SAA 7165)                                                                                                                                                                                                                                                        |                          |

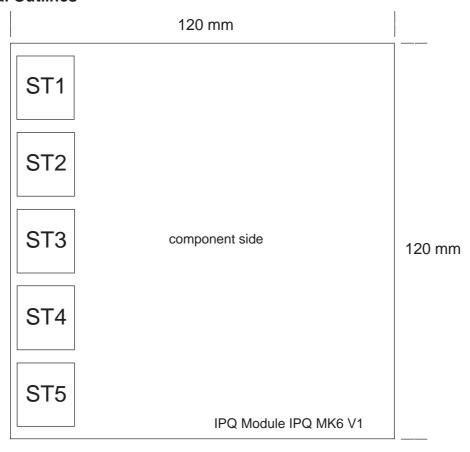

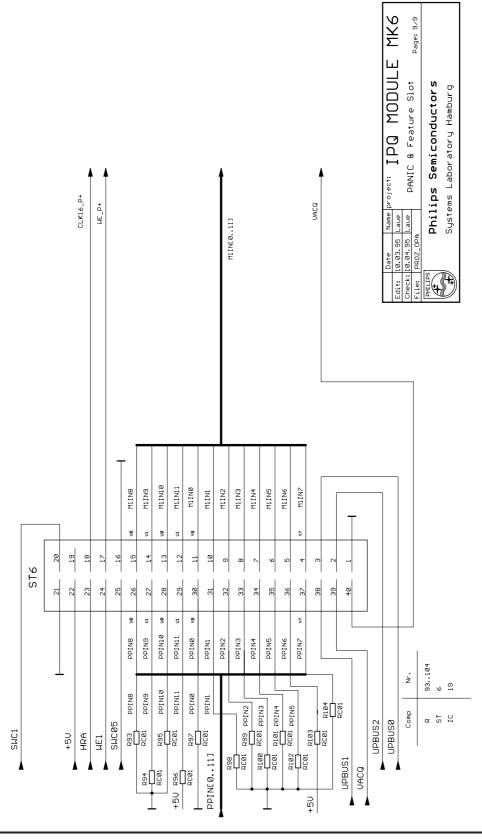

| 9.  | Interfa             | ace Signal                                                                                                                     | s IPQ Module                                                                                                                                                                                                                                                                | 45                       |

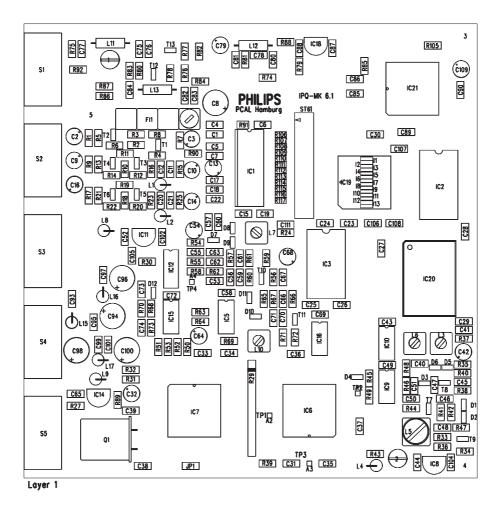

| 10. | Mecha               | nical Outl                                                                                                                     | ines                                                                                                                                                                                                                                                                        | 47                       |

| 11. | Alignn              | nent                                                                                                                           |                                                                                                                                                                                                                                                                             | 47                       |

| 12. | Useful              | hints                                                                                                                          |                                                                                                                                                                                                                                                                             | 48                       |

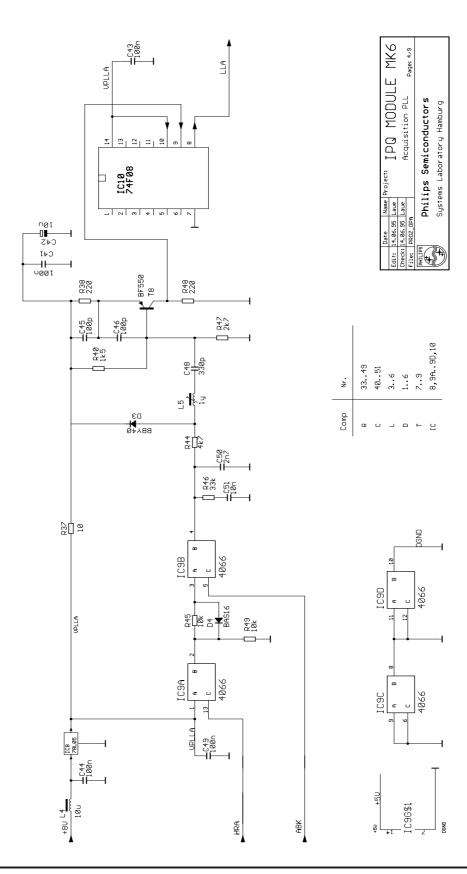

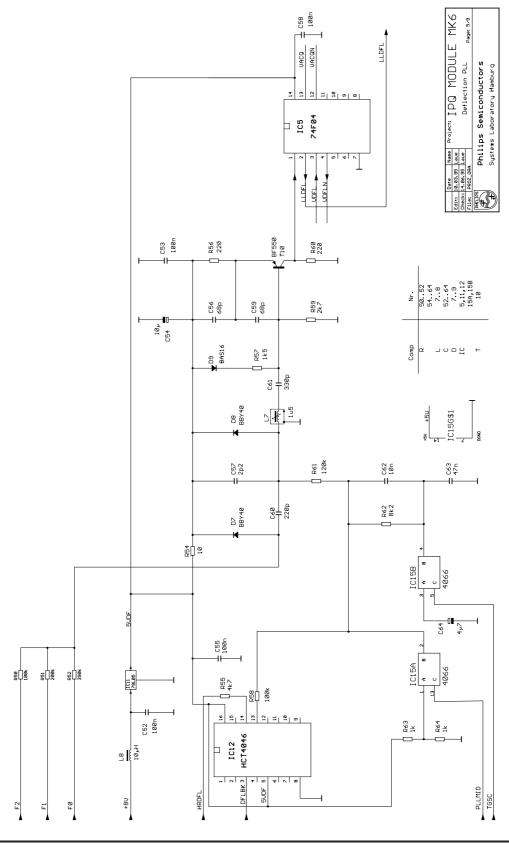

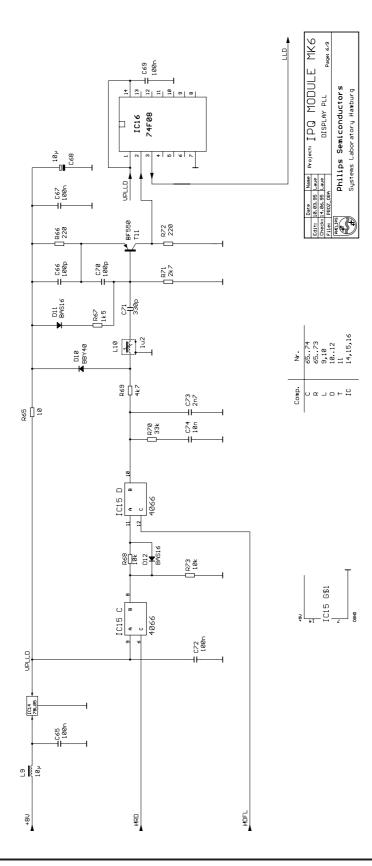

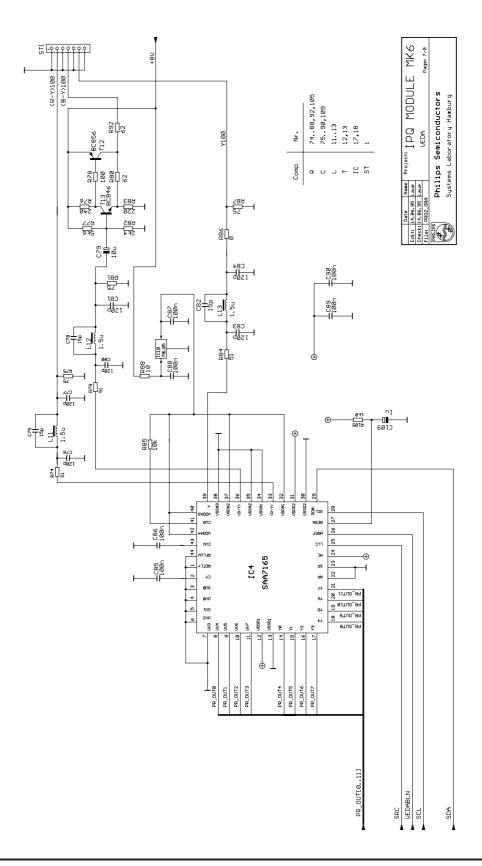

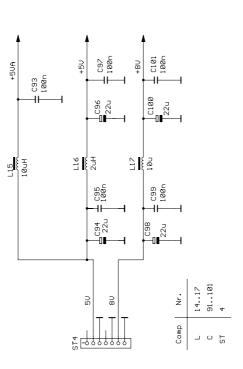

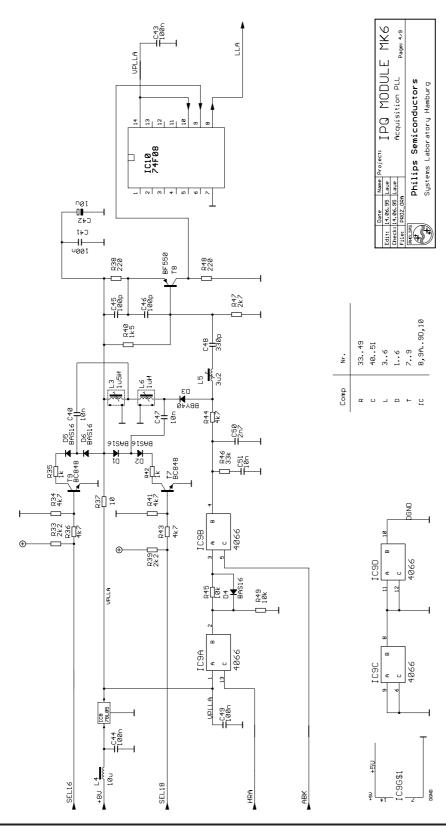

| 13. | IPQ M               | odule MK6                                                                                                                      | 5 V1 circuit diagrams                                                                                                                                                                                                                                                       | 49                       |

| 14. | Modifi              | ed circuit                                                                                                                     | parts for the IPQ application without Panoramic IC                                                                                                                                                                                                                          |                          |

|     |                     |                                                                                                                                |                                                                                                                                                                                                                                                                             |                          |

|     |                     | •                                                                                                                              |                                                                                                                                                                                                                                                                             |                          |

|     |                     |                                                                                                                                |                                                                                                                                                                                                                                                                             |                          |

#### 1. Introduction

#### 1.1 Definitions, Acronyms and Abbreviations

| IPQ μC   | Improved Picture Quality slave microcontroller             |

|----------|------------------------------------------------------------|

| HEX      | Hexadecimal program file                                   |

| ECO4     | Economy Controller IC 4                                    |

| SNERT    | Synchronous No parity Eight bit Reception and Transmission |

| PANIC    | Panorama IC                                                |

| PROZONIC | Progressive Scan Zoom and Noise Reduction IC               |

| VEDA     | Video Enhancement Digital to Analog Converter              |

| VDFL     | Vertical deflection pulse                                  |

| HDFL     | Horizontal deflection pulse                                |

| FRS      | Functional Requirements Spec                               |

#### 1.2 References

- [1] SCP Philips Semiconductors Software Creation Process, Wilko van Asseldonk, Marc De Smet, 9.4.96, V1.0

- [2] The IIC-bus and how to use it, 12 NC-No.: 9398 393 40011

- [3] SNERT bus specification see application note AN95127

- [4] S87C654 (μC) data sheet, Philips Semiconductors

- [5] TDA 8755 (ADC) data sheet, Philips Semiconductors

- [6] SAA 4952 (ECO4) data sheet, Philips Semiconductors

- [7] SAA 7165 (VEDA) data sheet, Philips Semiconductors

- [8] SAA 4995 (PANIC) data sheet, Philips Semiconductors

- [9] SAA 4990 (PROZONIC) data sheet, Philips Semiconductors

- [10] TMS 4C2970 (field memory) data sheet, Texas Instruments

- [11] TDA 9151, TDA 9152 (Deflection processor) data sheet, Philips Semiconductors

- [12] Data Handbook, Fast TTL Logic Series, IC 15, Philips Semiconductors

- [13] Data Handbook, High-speed CMOS logic family, IC 6, Philips Semiconductors

- [14] PAL plus Decoding using SAA4996 and SAA4997, Application note AN95126, Philips Semiconductors

# Application Note AN97017

#### 2. Hardware description

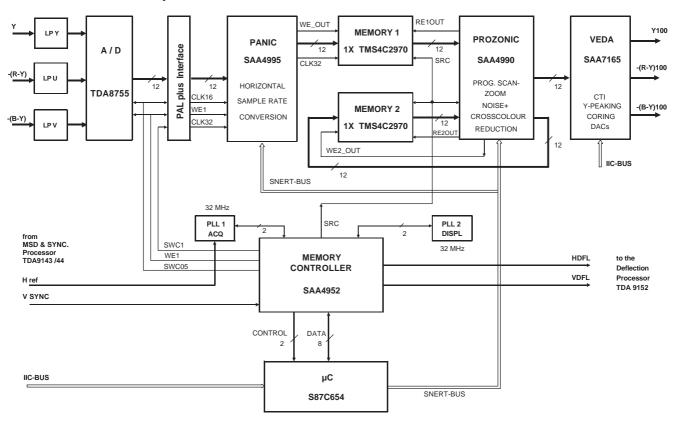

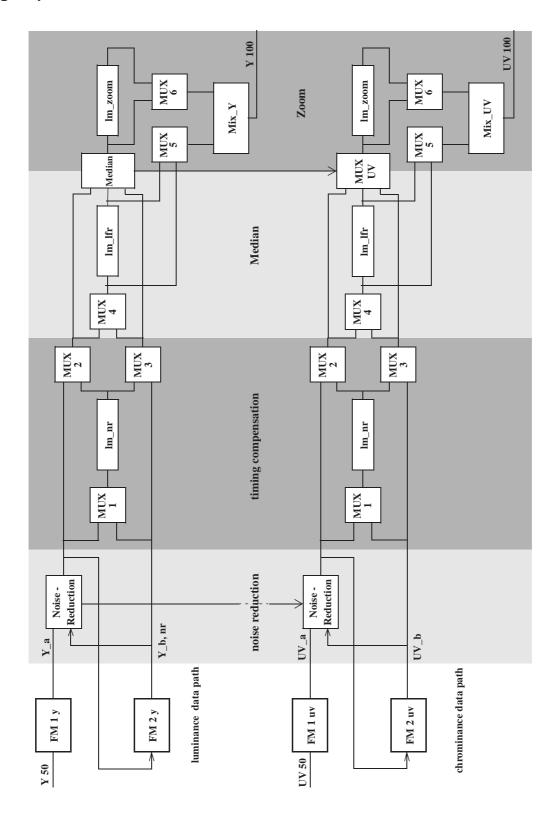

File: BLOCKD\_1.WMF / 97-01-06 Ke.

Fig.1 Blockdiagram of the IPQ Module with PANIC

The MK6V1 module is prepared to support different system configurations. Always two field memories are implemented. The video data is written into memory 1 [9] and read twice. At the output of memory 1 the field frequency is doubled to 100 / 120 Hz. The data is fed via the progressive scan, zoom and noise reduction IC PROZONIC [9] to the video enhancement and DA converter VEDA [7]. The VEDA IC performs an upconversion of the data rate from 4:1:1 (or 4:2:2) to 4:4:4 before the DA conversion is done. Furthermore a digital colour transient improvement, a luminance peaking and a coring function can be activated via I<sup>2</sup>C bus by the user.

For a simple field repetition mode the data can be reconverted to analog output signals without additional processing in front of the SAA 7165. If the line flicker reduction (LFR), progressive scan or zoom feature is active the information is written into field memory 2 [9]. This memory works as a 50 / 60 Hz field delay. By the help of this second field memory PROZONIC is able to process information of a whole frame, e.g. PROZONIC

- calculates the median filtered fields A\* and B\* in the sequence AA\*B\*B for field rate upconversion with LFR.

- b) calculates the median filtered lines odd and even for progressive scan conversion,

- c) averages between incoming and previous fields for the adaptive noise and cross-colour reduction obtained by a recursive filter in the 2 fh domain and

- d) interpolates lines for the vertical zoom function or progressive scan.

# Application Note AN97017

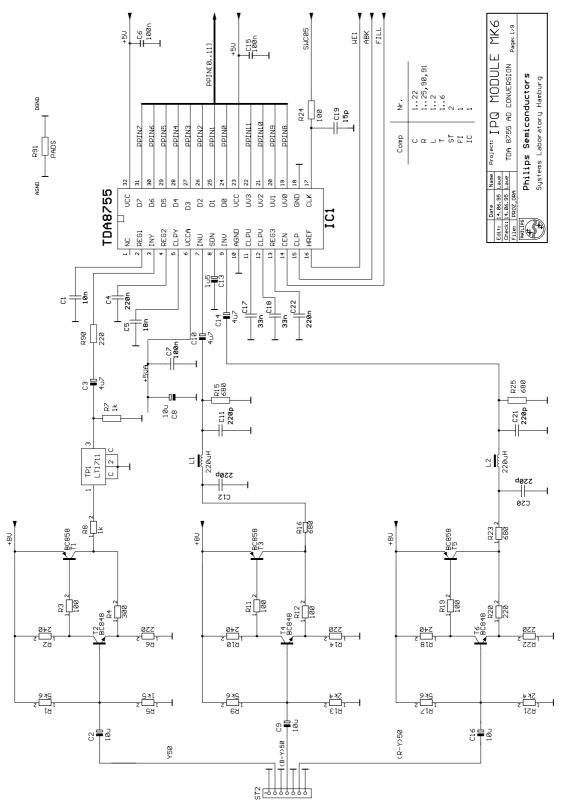

If a scan converter is used along with an analog colour decoder frontend an AD-Converter is necessary to convert the three baseband input signals Y, -(R-Y) and -(B-Y). Those signals are preamplified and low pass filtered to avoid antialiasing effects.

The 8 bit triple AD-Converter TDA8755 [5], applied in this IPQ module, has an integrated clamping function and is equipped with a data formatter. The data formatter converts the signal data provided by the AD conversion into a 12 bit data format, 8 bit for luminance and 4 bit for the serial chrominance output data format (bandwidth ratio Y:U:V = 4:1:1). These data are supplied to the digital data output bus of 12 bits width.

The SAA 4995 (PANorama IC) is an add-on device to be used between AD-Converter and the first field memory. It performs:

- a) a linear horizontal sample rate conversion with the capability to zoom and compress the picture with a conversion rate between 0.5 and 2.

- b) a dynamic sample rate conversion for a panorama display of e.g. 4:3 picture material on a 16:9 display without side panels.

In panorama mode the sample rate conversion factor is modulated along the video line. For the panorama function the picture is compressed in horizontal direction in the middle of the screen and zoomed at the sides. It is also possible to program the inverted function. The PANIC has to be supplied with 16 MHz and also the double frequency of 32 MHz which is used for the sample rate conversion filter. The field memory 1 is supplied with a writing clock of 32 MHz. The WEout of PANIC determines when a pixel shall be written. In a normal mode without compression or zoom the logical status of the WE signal will change from clock to clock. If a zoom factor of two is active the WE signal will remain in the logical high status for the whole active line.

The acquisition PLL generates the 32 MHz writing clock. The display PLL which is intended to have a large time constant and a small tracking range (+/- 6 %) is generating the 32 MHz display clock. A double clock system has advantages if an unstable source like a VCR is connected to a 100 Hz converter.

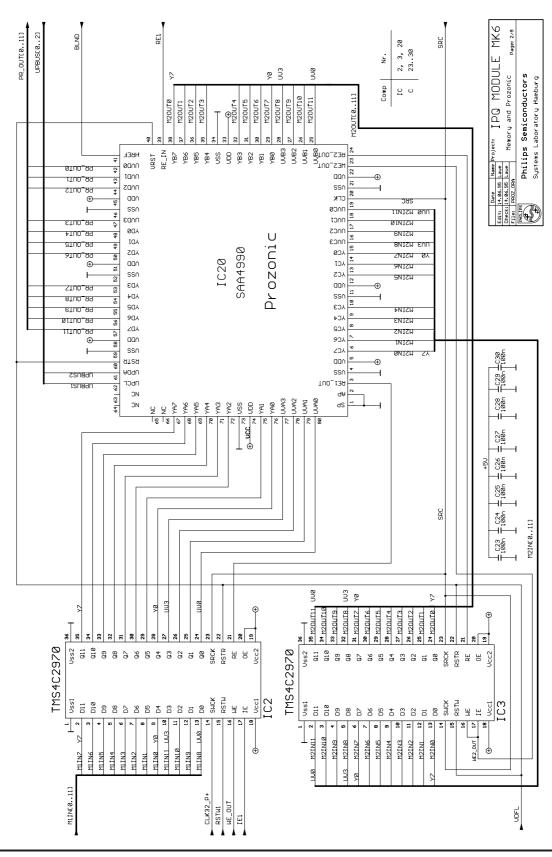

All control signals to run the module and reference signals for the PLLs are generated by the SAA 4952 [6]. The memory controller itself is controlled by a microcontroller S87C654 or S87C652 via an 8 bit parallel interface [4]. Every vertical blanking period of the display is used to transmit the desired register settings to the SAA4952 dependent on the chosen mode of the module. Additionally the microcontroller communicates via a three wire SNERT bus interface [3] with the PANIC and PROZONIC.

Besides the 100 Hz / 120 Hz conversion it is also possible to run a progressive scan mode. In this case the reading of the memories is changed to 50 / 60 Hz field frequency. The inserted lines are generated by median processing in the PROZONIC IC. Also this conversion mode can be combined with the vertical zoom function and in contrast to the 100 Hz mode it is also possible to realize a vertical compression.

The synchronization of the module is obtained by providing a vertical synchronization signal  $50/60\,$  Hz and a horizontal synchronization signal  $15.625/15.750\,$  kHz. The latter can e.g. consist of clamping pulses or line blanking pulses. The software can adapt the internal field recognition in the memory controller to any synchronization pulse (H to V) timing condition.

The various modes of the IPQ module are activated via a simple IIC-Interface [2] of the microcontroller on the board.

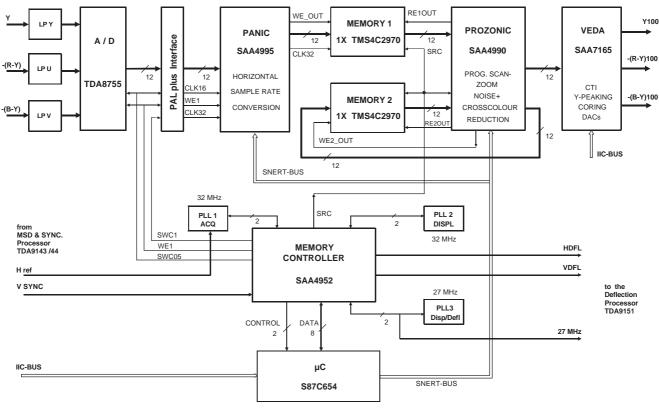

File: BLOCKD\_2.WMF / 97-01-06 Ke.

Fig.2 Blockdiagram of the IPQ Module containing PANIC and an additional display PLL to drive the Deflection Processor TDA9151.

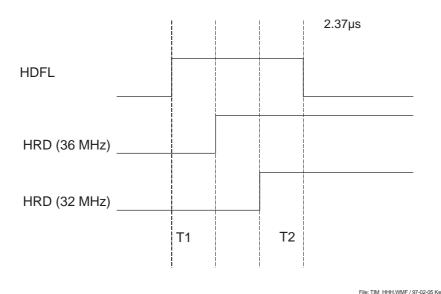

The IPQ application of Figure 2 assumes that a TDA 9151 is used as Deflection Processor. This device needs a 27MHz linelocked clock signal. Compared to the system explained before an additional 27 MHz PLL has to be implemented. The 32 MHz display PLL is locked to the horizontal deflection pulse HDFL from the memory controller. The 27 MHz deflection PLL is coupled to the externally provided Href signal. The tracking range and the bandwidth of this PLL has been restricted to ensure a good jitter (high frequent time base distortions) suppression. Thus a stable linelocked clock signal generation is given even at Href signals with a poor time base stability. The 32 MHz display PLL is coupled to the horizontal deflection pulse HDFL. Its tracking range and bandwidth is larger compared with the deflection PLL to achieve a fast and perfect synchronization between the deflection and the display data read from the memories.

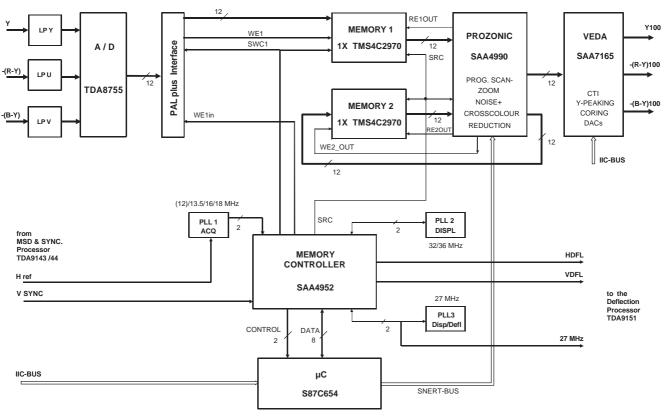

File: BLOCKD\_3.WMF / 97-01-06 Ke.

Fig.3 Blockdiagram of the IPQ Module without PANIC, containing a additional Display PLL to drive the Deflection Processor TDA9151.

The IPQ application in figure 3 does not include the SAA 4995 (PANIC). The different horizontal zoom and compression ratios are realized by the combinations of writing to reading frequency of the memories. The acquisition PLL can generate the following frequencies: (12), 13.5, 16 and 18 MHz. This PLL uses a VCO whose frequency is switched to the desired frequency. As display frequencies 27, 32 and 36 MHz are supported. The PLL2 is not switched. It is able to generate 32 MHz as well as 36 MHz.

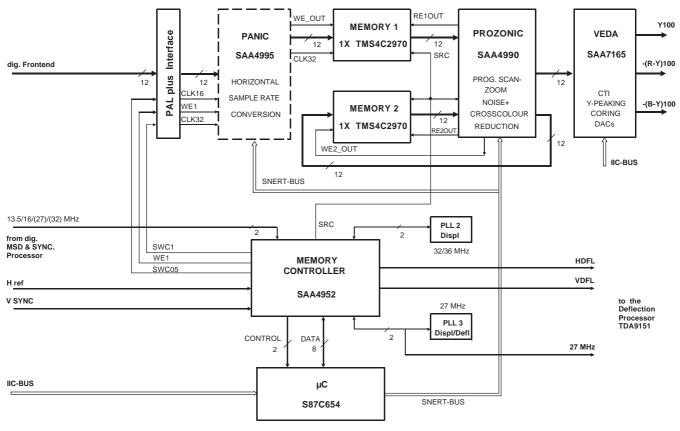

File: BLOCKD\_4.WMF /97-01-06 Ke

Fig.4 Block diagram of the IPQ Module for direct signal supply from a digital Multi-Standard Decoder and Sync. Processor IC.

The block diagram above shows the IPQ module implemented in a system with a digital colour decoder. In this case a clock signal provided by the digital decoder is used as acquisition clock. The memory controller is supplied with a horizontal reference pulse used to reset the H-counters in the SAA 4952. The digital data bus can directly be connected to the PANIC or to the first field memory if the PANIC is not implemented. If the deflection processor TDA 9151 is used, the display PLL 2 is necessary. This additional PLL can be left out when the TDA 9152 is used instead of TDA 9151.

If the user does not want to use the benefits of a double clock system, it is also possible to supply the whole system with a clock of 27 or 32 MHz. In this case no external PLL circuits are required. The controlling of the SAA 4952 can be adapted to this configuration by a special software.

#### 3. Signal path of the SAA 4990 PROZONIC

Fig.5 Main signal paths of PROZONIC

# Application Note AN97017

The block diagram of figure 5 shows the main signal paths of PROZONIC. The first processing block, directly connected to the field memories, is the noise reduction. The reading of the memories has to be adapted to the demands of the noise reduction timing in order to ensure that the same pairs of adjacent lines of a frame can be processed every 100 Hz field. If necessary also the signal data from one of the memories can be delayed by one line (lm\_nr), thus the adjacent lines out of two fields are supplied into the following median filter block. The line memory lm\_lfr is needed as a line delay for the median filter, which filters two adjacent lines from one field and the line in between from the other field. The settings of the multiplexers are defined by the software control. These settings are dependent on the selected field control mode and the field to be processed. The last processing part is the zoom block. The mixer can mix information from two lines with weighting factors. The input lines can contain median filtered and original unfiltered information.

#### 4. General software description

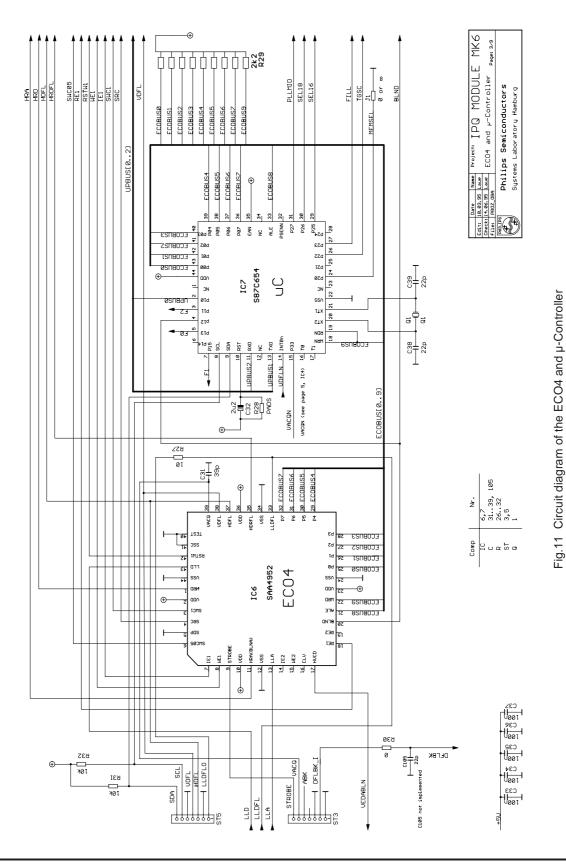

The specification describes the functional requirements of an IPQ S87C654/P83C654FBA slave microcontroller software [1]. The slave IPQ  $\mu$ C is used as an interpreter between a main (master)  $\mu$ C and the ICs ECO4 (SAA4952), PANIC (SAA 4995) and PROZONIC (SAA 4990).

The IPQ  $\mu$ C reads up to 22 register bytes via the I<sup>2</sup>C bus from the master  $\mu$ C and sends itself 3 read bytes (1 status byte and 2 movie phase detection bytes) whenever addressed with R/W = 1. The I<sup>2</sup>C register bytes are written into the  $\mu$ Cs RAM.

After the evaluation of data and following VDFL the IPQ  $\mu$ C sends data to ECO4 on port P0 (parallel), to PANIC and PROZONIC via the SNERT interface running in mode 0.

The VEDA is controlled directly via I2C-bus.

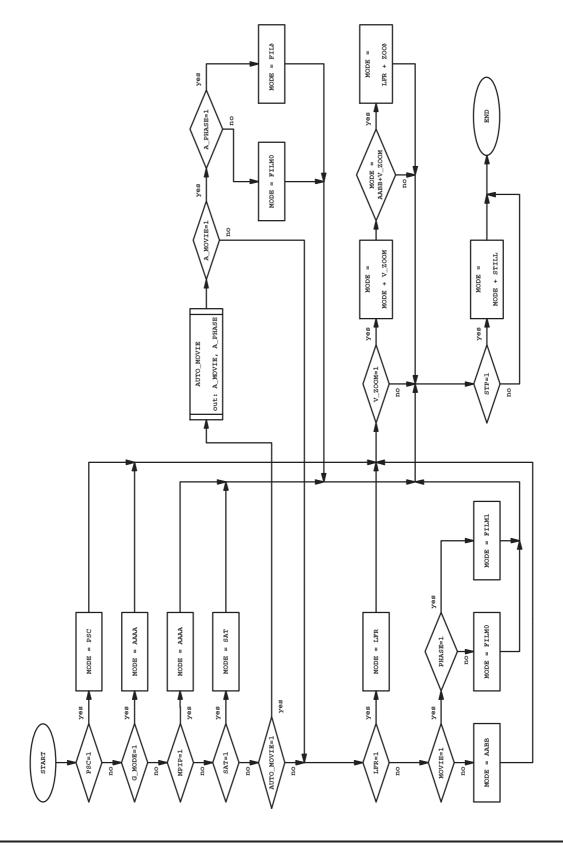

#### 4.1 Main functional flow chart

After power-on reset the  $\mu$ -controller performs an initialization. Romtable values are copied into RAM, control mode flags/variables are set/cleared. The VDFL interrupt has the highest priority. After initialization the main program waits for an occurring interrupt. During the initialization phase (after power on reset) the first VDFL interrupt is initiated by software.

After a VDFL interrupt has occurred on the  $\mu$ C port pin INT0N, the field number is read by the IPQ  $\mu$ C from the SAA 4952. Then the data transmission to PANIC, ECO4 and PROZONIC is performed. If the internal MPIP is used in an IPQ concept without PANIC (SAA 4995) the  $\mu$ -controller is interrupted by the vertical acquisition synchronization pulse VACQ at INT1N instead of VDFL. This interrupt is also used in the generator mode. The field length of the display is constant and independent from the source if this option is active.

$^{12}$ C input registers received during slave receiver operation are read and evaluated according to different priorities. The INIT bit in REG2 has the highest priority. If this bit is set, an initialization of ECO4/PANIC/PROZONIC with default values out of the  $\mu$ Cs ROM table is done immediately. After VDFL interrupt handling,  $^{12}$ C interrupts can be serviced.

The I<sup>2</sup>C bus interrupt routine handles the reception of the register bytes from the master  $\mu$ C as well as the transmission of the status byte plus movie detection bytes.

The following flow chart shows the priority structure of the field control modes. The generator mode has the highest priority, followed by Multi PIP, Progressive Scan Mode and Sat Mode. The next levels in priority are the Auto-Movie Processing, the LFR Mode and on the lowest level the field repetition mode. The field control modes are described in detail in chapter 6.

Fig.6 Software flow chart showing the priority structure of the field control modes

# Application Note AN97017

#### 5. I2C-bus interface

#### 5.1 Definition of the interface

The interface of the IPQ µC is realized with a hardware I2C bus [2].

The slave address of the IPQ µC is 68h:

Slave address = 0 1 1 0 1 0 0 R/W

The IPQ  $\mu$ C can either act as a slave receiver or a slave transmitter. In the slave receiver mode the IPQ  $\mu$ C reads I²C register data bytes from the main controller which then acts as a master transmitter. In the slave transmitter mode the IPQ  $\mu$ C sends status information plus 2 movie detection bytes to the main  $\mu$ C which works as a master receiver reading the byte information.

#### 5.2 Sending data to the IPQ μC

#### 5.2.1 I<sup>2</sup>C transmission protocol

The transmission protocol has the following format:

| Start | Slave address | Ack | REG1 | Ack |  | Ack | REG22 | Ack | Stop |

|-------|---------------|-----|------|-----|--|-----|-------|-----|------|

|-------|---------------|-----|------|-----|--|-----|-------|-----|------|

After having addressed the IPQ  $\mu$ C with its slave address the master  $\mu$ C transmits up to 22 register bytes over the I<sup>2</sup>C bus.

The control of some functions is different dependent on the fact whether the SAA 4995 (PANIC) is part of the system or not. Therefore this case the relevant I<sup>2</sup>C registers are listed twice, with PANIC and without PANIC.

#### I<sup>2</sup>C register data format

TABLE 1 I<sup>2</sup>C-Register REG1 (Conversion mode selection)

| Bit | Name           | Function                                                                 |

|-----|----------------|--------------------------------------------------------------------------|

| 0   | PSC            | 0: Progressive scan mode off 1: Progressive scan mode on                 |

| 1   | GENERATOR_MODE | 0: normal mode<br>1: Generator mode on (312,5 lines / field continually) |

| 2   | SAT            | 0: Satellite mode off<br>1: Satellite mode on (A*A*B*B*)                 |

| 3   | reserved       |                                                                          |

# Application Note AN97017

#### TABLE 1 I<sup>2</sup>C-Register REG1 (Conversion mode selection)

| Bit | Name        | Function                                                                                                                                                                                      |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | AUTO_MOVIE  | O: movie detection disabled 1: automatic movie source detection activated. In case a movie mode is detected, a movie will be processed (MOVIE, MOVIE_PHASE are readable via STATUS register). |

| 5   | LFR         | O: Line Flicker Reduction mode off     1: Line Flicker Reduction mode on                                                                                                                      |

| 6   | MOVIE       | 0: forced MOVIE mode off<br>1: forced MOVIE mode on                                                                                                                                           |

| 7   | MOVIE_PHASE | forced phase flag to be set in combination with MOVIE: 0: normal (ABAB) 1: 180° phase shift (BCBC)                                                                                            |

#### TABLE 2 I<sup>2</sup>C-Register REG2 (Field control)

| Bit | Name     | Function                                                                                        |                                                   |                  |  |  |  |

|-----|----------|-------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------|--|--|--|

| 0   | PP0      | picture p                                                                                       | picture position bit 0                            |                  |  |  |  |

| 1   | PP1      | picture p                                                                                       | osition bit 1                                     |                  |  |  |  |

|     |          | PP1                                                                                             | PP0                                               | picture position |  |  |  |

|     |          | 0                                                                                               | 0                                                 | centre           |  |  |  |

|     |          | 0                                                                                               | 1                                                 | max. left        |  |  |  |

|     |          | 1                                                                                               | 0                                                 | max right        |  |  |  |

| 2   | AFF      | acquisition field frequency (50/60 Hz): 0: 50 Hz 1: 60 Hz                                       |                                                   |                  |  |  |  |

| 3   | STP      | still picture mode: 0: off 1: on (one field out of AABB, full frame median filtered out of LFR) |                                                   |                  |  |  |  |

| 4   | reserved |                                                                                                 |                                                   |                  |  |  |  |

| 5   | reserved |                                                                                                 |                                                   |                  |  |  |  |

| 6   | reserved |                                                                                                 |                                                   |                  |  |  |  |

| 7   | INIT     | initialize                                                                                      | initialize ECO4, PROZONIC, PANIC: 0 = off, 1 = on |                  |  |  |  |

TABLE 3 I<sup>2</sup>C-Register REG3 (Vertical Zoom, Field control) (without PANIC)

| Bit | Name     | Fund  | Function            |        |         |                       |  |  |

|-----|----------|-------|---------------------|--------|---------|-----------------------|--|--|

| 0   | VZOOM_0  | Verti | Vertical zoom bit 0 |        |         |                       |  |  |

| 1   | VZOOM_1  | Verti | Vertical zoom bit 1 |        |         |                       |  |  |

| 2   | VZOOM_2  | Verti | cal zo              | om bit | 2       |                       |  |  |

|     |          | V2    | V1                  | V0     | Conv    | ersion factor         |  |  |

|     |          | 0     | 0                   | 0      | no Zo   | oom                   |  |  |

|     |          | 0     | 0                   | 1      | 1,1     |                       |  |  |

|     |          | 0     | 1                   | 0      | 1,25    |                       |  |  |

|     |          | 0     | 1                   | 1      | 1,33    |                       |  |  |

|     |          | 1     | 0                   | 0      | 1,5     |                       |  |  |

|     |          | 1     | 0                   | 1      | reser   | ved                   |  |  |

|     |          | 1     | 1                   | 0      | reser   | ved                   |  |  |

|     |          | 1     | 1                   | 1      | reser   | ved                   |  |  |

| 3   | reserved |       | ,                   | •      | 1       |                       |  |  |

| 4   | FSA0     | frequ | iency               | select | acquis  | ition bit 0           |  |  |

| 5   | FSA1     | frequ | iency               | select | acquis  | ition bit 1           |  |  |

|     |          | FSA   | 1                   | FSAC   | )       | acquisition frequency |  |  |

|     |          | 0     |                     | 0      |         | 12 MHz                |  |  |

|     |          | 0     |                     | 1      |         | 13.5 MHz              |  |  |

|     |          | 1     |                     | 0      |         | 16 MHz                |  |  |

|     |          | 1     |                     | 1      |         | 18 MHz                |  |  |

| 6   | FSD0     | frequ | iency               | select | display | bit 0                 |  |  |

| 7   | FSD1     | frequ | iency               | select | display | bit 1                 |  |  |

|     |          | FSD   | 1                   | FSD    | )       | display frequency     |  |  |

|     |          | 0     |                     | Х      |         | 27 Mhz                |  |  |

|     |          | 1     |                     | 0      |         | 32 MHz                |  |  |

|     |          | 1     |                     | 1      |         | 36 MHz                |  |  |

#### TABLE 4 I<sup>2</sup>C-Register REG3 (Vertical Zoom) (with PANIC)

| Bit | Name     | Function            |                     |        |                   |  |  |

|-----|----------|---------------------|---------------------|--------|-------------------|--|--|

| 0   | VZOOM_0  | Vertical zoom bit 0 |                     |        |                   |  |  |

| 1   | VZOOM_1  | Verti               | cal zo              | om bit | 1                 |  |  |

| 2   | VZOOM_2  | Verti               | Vertical zoom bit 2 |        |                   |  |  |

|     |          | V2                  | V1                  | V0     | Conversion factor |  |  |

|     |          | 0                   | 0                   | 0      | no Zoom           |  |  |

|     |          | 0                   | 0                   | 1      | 1,1               |  |  |

|     |          | 0                   | 1                   | 0      | 1,25              |  |  |

|     |          | 0                   | 1                   | 1      | 1,33              |  |  |

|     |          | 1                   | 0                   | 0      | 1,5               |  |  |

|     |          | 1                   | 0                   | 1      | reserved          |  |  |

|     |          | 1                   | 1                   | 0      | reserved          |  |  |

|     |          | 1                   | 1                   | 1      | reserved          |  |  |

| 3   | reserved |                     |                     |        |                   |  |  |

| 4   | reserved |                     |                     |        |                   |  |  |

| 5   | reserved |                     |                     |        |                   |  |  |

| 6   | reserved |                     |                     |        |                   |  |  |

| 7   | reserved |                     |                     |        |                   |  |  |

#### TABLE 5 I<sup>2</sup>C-Register REG4 (Internal MPIP control) (without PANIC)

| Bit | Name     | Function                              |

|-----|----------|---------------------------------------|

| 0   | POS0     | PIP position bit 0                    |

| 1   | POS1     | PIP position bit 1                    |

| 2   | POS2     | PIP position bit 2                    |

| 3   | POS3     | PIP position bit 3                    |

| 4   | NPIP_4x4 | 0: no 4x4 PIPs, take NPIP 1: 4x4 PIPs |

# Application Note AN97017

#### TABLE 5 I<sup>2</sup>C-Register REG4 (Internal MPIP control) (without PANIC)

| Bit | Name | Function                               |

|-----|------|----------------------------------------|

| 5   | NPIP | number of PIPs 0: 3x3 PIPs 1: 4x3 PIPs |

| 6   | MPIP | 0: Multi-PIP off<br>1: Multi-PIP on    |

| 7   | SPIP | NTSC PIP: 0: 50 Hz PIP 1: 60 Hz PIP    |

#### TABLE 6 I<sup>2</sup>C-Register REG4 (External MPIP control) (with PANIC)

| Bit | Name     | Function                                  |

|-----|----------|-------------------------------------------|

| 0   | POS0     | PIP position bit 0                        |

| 1   | POS1     | PIP position bit 1                        |

| 2   | POS2     | PIP position bit 2                        |

| 3   | POS3     | PIP position bit 3                        |

| 4   | NPIP_4x4 | 0: no 4x4 PIPs, take NPIP<br>1: 4x4 PIPs  |

| 5   | NPIP     | number of PIPs 0: 3x3 PIPs 1: 4x3 PIPs    |

| 6   | MPIP     | 0: Multi-PIP off<br>1: Multi-PIP on       |

| 7   | SPIP     | NTSC PIP:<br>0: 50 Hz PIP<br>1: 60 Hz PIP |

TABLE 7 I2C-Register REG5 (Noise reduction, split screen, screen fade, ect.)

| Bit | Name          | Function                                                             | Function              |                 |  |  |  |

|-----|---------------|----------------------------------------------------------------------|-----------------------|-----------------|--|--|--|

| 0   | NR0           | noise reduction bit 0                                                |                       |                 |  |  |  |

| 1   | NR1           | noise redu                                                           | noise reduction bit 1 |                 |  |  |  |

|     |               | NR0                                                                  | NR1                   | noise reduction |  |  |  |

|     |               | 0                                                                    | 0                     | off             |  |  |  |

|     |               | 0                                                                    | 1                     | low             |  |  |  |

|     |               | 1                                                                    | 0                     | middle          |  |  |  |

|     |               | 1                                                                    | 1                     | high            |  |  |  |

| 2   | SPS0          | split scree                                                          | en bit 0              |                 |  |  |  |

| 3   | SPS1          | split screen bit 1                                                   |                       |                 |  |  |  |

|     |               | SPS1                                                                 | SPS0                  | split screen    |  |  |  |

|     |               | 0                                                                    | Х                     | off             |  |  |  |

|     |               | 1                                                                    | 0                     | horizontal      |  |  |  |

|     |               | 1                                                                    | 1                     | vertical        |  |  |  |

| 4   | SCF0          | screen fade bit 0 (not yet implemented)                              |                       |                 |  |  |  |

| 5   | SCF1          | screen fac                                                           | de bit 1 (not y       | et implemented) |  |  |  |

|     |               | SCF1                                                                 | SCF1                  | screen fade     |  |  |  |

|     |               | 0                                                                    | Х                     | off             |  |  |  |

|     |               | 1                                                                    | 0                     | fade in         |  |  |  |

|     |               | 1                                                                    | 1                     | fade out        |  |  |  |

| 6   | ENA_LFR_PHASE | 0: fixed mode     1: adaptive control of LFR phase for movie sources |                       |                 |  |  |  |

| 7   |               | reserved                                                             |                       |                 |  |  |  |

#### TABLE 8 I<sup>2</sup>C-Register REG6 (HWE1 delay)

| Bit | Name   | Function                                |

|-----|--------|-----------------------------------------|

| 0   | HWE1F0 | HWE1 fine delay offset to default, bit0 |

| 1   | HWE1F1 | HWE1 fine delay offset to default, bit1 |

| 2   | HWE1F2 | HWE1 fine delay offset to default, bit2 |

| 3   | HWE1F3 | HWE1 fine delay offset to default, bit3 |

| 4   | HWE1F4 | HWE1 fine delay offset to default, bit4 |

| 5   | HWE1F5 | HWE1 fine delay offset to default, bit5 |

| 6   | HWE1F6 | HWE1 fine delay offset to default, bit6 |

| 7   | HWE1F7 | HWE1 fine delay offset to default, bit7 |

#### TABLE 9 I<sup>2</sup>C-Register REG7 (Vertical shift)

| Bit | Name   | Function                                                                       |

|-----|--------|--------------------------------------------------------------------------------|

| 0   | VWE1D0 | VWE1 delay bit 0                                                               |

| 1   | VWE1D1 | VWE1 delay bit 1                                                               |

| 2   | VWE1D2 | VWE1 delay bit 2                                                               |

| 3   | VWE1D3 | VWE1 delay bit 3                                                               |

| 4   | VWE1D4 | VWE1 delay bit 4                                                               |

| 5   | VWE1D5 | VWE1 delay bit 5                                                               |

| 6   | VWE1D6 | VWE1 delay bit 6                                                               |

| 7   | VWE1X  | 0: off, normal mode 1: on, vertical write window upwards shiftable by VWE1D0D6 |

#### TABLE 10 I<sup>2</sup>C-Register REG8

| Bit | Name        | Function                                                                                   |

|-----|-------------|--------------------------------------------------------------------------------------------|

| 0   | SET_HOR_DEL | 0: normal mode: HOR_DELAYS = 0 1: HOR_DELAYS value taken from REG12 direct PROZONIC access |

| 1   | SET_HDDEL   | 0: normal mode 1: take HDDEL setting from REG 13                                           |

| 2   | SET_HD      | 0: normal mode 1: set HDSTA/STO ECO4 values direct via IIC REGs 14, 15                     |

| 3   | SET_VD      | 0: normal mode 1: set VDSTA/STO ECO4 values direct via IIC REGs 16, 17                     |

| 4   | SET_MSB     | 0: normal mode 1: take MSB setting from REG 18                                             |

| 5   | reserved    |                                                                                            |

| 6   | reserved    |                                                                                            |

| 7   | reserved    |                                                                                            |

#### TABLE 11 I<sup>2</sup>C-Register REG9 (Port bit control)

| Bit | Name     | Function                                    |

|-----|----------|---------------------------------------------|

| 0   | reserved |                                             |

| 1   | P11      | 0: clear port bit P1.1 1: set port bit P1.1 |

| 2   | reserved |                                             |

| 3   | P13      | 0: clear port bit P1.3 1: set port bit P1.3 |

| 4   | P15      | 0: clear port bit P1.5 1: set port bit P1.5 |

| 5   | P34      | 0: clear port bit P3.4 1: set port bit P3.4 |

| 6   | P35      | 0: clear port bit P3.5 1: set port bit P3.5 |

| 7   | P14      | 0: clear port bit P1.4 1: set port bit P1.4 |

#### TABLE 12 I<sup>2</sup>C-Register REG10: (Blank fields) (without PANIC)

| Bit | Name     | Function      |

|-----|----------|---------------|

| 0   | BLANK_F0 | Blank field 0 |

| 1   | BLANK_F1 | Blank field 1 |

| 2   | BLANK_F2 | Blank field 2 |

| 3   | BLANK_F3 | Blank field 3 |

| 4   | reserved |               |

| 5   | reserved |               |

| 6   | reserved |               |

| 7   | reserved |               |

#### TABLE 13 I<sup>2</sup>C-Register REG10: (Blank fields, PANIC control) (with PANIC)

| Bit | Name     | Function            |

|-----|----------|---------------------|

| 0   | BLANK_F0 | Blank field 0       |

| 1   | BLANK_F1 | Blank field 1       |

| 2   | BLANK_F2 | Blank field 2       |

| 3   | BLANK_F3 | Blank field 3       |

| 4   | PANIC_0  | PANIC control bit 0 |

| 5   | PANIC_1  | PANIC control bit 1 |

| 6   | PANIC_2  | PANIC control bit 2 |

| 7   | PANIC_3  | PANIC control bit 3 |

# Application Note AN97017

TABLE 13 I<sup>2</sup>C-Register REG10: (Blank fields, PANIC control) (with PANIC)

| Bit | Name | Fun    | ction  |    |    |                                       |

|-----|------|--------|--------|----|----|---------------------------------------|

|     |      | P<br>3 | P<br>2 | P1 | P0 | mode                                  |

|     |      | 0      | 0      | 0  | 0  | normal mode                           |

|     |      | 0      | 0      | 0  | 1  | hor. zoom factor 1,1                  |

|     |      | 0      | 0      | 1  | 0  | hor. zoom factor 1,25                 |

|     |      | 0      | 0      | 1  | 1  | hor. zoom factor 1,33                 |

|     |      | 0      | 1      | 0  | 0  | hor. zoom factor 1,5                  |

|     |      | 0      | 1      | 0  | 1  | hor. zoom factor 2                    |

|     |      | 0      | 1      | 1  | 0  | reserved                              |

|     |      | 0      | 1      | 1  | 1  | reserved                              |

|     |      | 1      | 0      | 0  | 0  | hor. lin. compress factor 1,33        |

|     |      | 1      | 0      | 0  | 1  | PANORAMA mode, high non-linearity     |

|     |      | 1      | 0      | 1  | 0  | PANORAMA mode, moderate non-linearity |

|     |      | 1      | 0      | 1  | 1  | reserved                              |

|     |      | 1      | 1      | 0  | 0  | reserved                              |

|     |      | 1      | 1      | 0  | 1  | reserved                              |

|     |      | 1      | 1      | 1  | 0  | reserved                              |

|     |      | 1      | 1      | 1  | 1  | reserved                              |

TABLE 14 I<sup>2</sup>C-Register REG11 (Port bit and 27MHz PLL control)

| Bit | Name       | Function                                    |

|-----|------------|---------------------------------------------|

| 0   | P20        | 0: clear port bit P2.0 1: set port bit P2.0 |

| 1   | P21        | 0: clear port bit P2.1 1: set port bit P2.1 |

| 2   | P22 (TGSC) | 0: clear port bit P2.2 1: set port bit P2.2 |

| 3   | P23 (FILL) | 0: clear port bit P2.3 1: set port bit P2.3 |

# Application Note AN97017

#### TABLE 14 I<sup>2</sup>C-Register REG11 (Port bit and 27MHz PLL control)

| Bit | Name         | Function                                        |

|-----|--------------|-------------------------------------------------|

| 4   | P24          | 0: clear port bit P2.4 1: set port bit P2.4     |

| 5   | reserved     |                                                 |

| 6   | reserved     |                                                 |

| 7   | PLLMID (P27) | 0: 27 MHz PLL locked 1: 27 MHz PLL free running |

#### TABLE 15 I<sup>2</sup>C-Register REG12 (Horizontal delay)

| Bit | Name       | Function                        |

|-----|------------|---------------------------------|

| 07  | HOR_DELAYS | direct PROZONIC register access |

#### TABLE 16 I<sup>2</sup>C-Register REG13 (Horizotal fine delay)

| Bit | Name  | Function                                                            |

|-----|-------|---------------------------------------------------------------------|

| 07  | HDDEL | direct ECO4 register access, fine delay of the hor. display signals |

#### TABLE 17 I<sup>2</sup>C-Register REG14 (Start value of HD signal)

| Bit | Name  | Function                                                  |  |

|-----|-------|-----------------------------------------------------------|--|

| 07  | HDSTA | direct ECO4 register access, start value of the HD signal |  |

#### TABLE 18 I<sup>2</sup>C-Register REG15 (Stop value of the HD signal)

| Bit | Name  | Function                                                 |

|-----|-------|----------------------------------------------------------|

| 07  | HDSTO | direct ECO4 register access, stop value of the HD signal |

# Application Note AN97017

#### TABLE 19 I<sup>2</sup>C-Register REG16 (Start value of the VD signal)

| Bit | Name  | Function                                                                                              |  |

|-----|-------|-------------------------------------------------------------------------------------------------------|--|

| 07  | VDSTA | direct ECO4 register access, start value of VD signal, vertical blanking for DAC via ECO4 signal HVCD |  |

#### TABLE 20 I<sup>2</sup>C-Register REG17 (Stop value of the VD signal)

| Bit | Name  | Function                                                     |  |

|-----|-------|--------------------------------------------------------------|--|

| 07  | VDSTO | direct ECO4 control register access, stop value of VD signal |  |

#### TABLE 21 I<sup>2</sup>C-Register REG18 (MSD control)

| Bit | Name      | Function                       |

|-----|-----------|--------------------------------|

| 0   | MSB_HDSTA | MSB of SAA 4952 HD start value |

| 1   | MSB_HDSTO | MSB of SAA 4952 HD stop value  |

| 2   | MSB_VDSTA | MSB of SAA 4952 VD start value |

| 3   | MSB_VDSTO | MSB of SAA 4952 VD stop value  |

| 47  | reserved  |                                |

#### TABLE 22 I<sup>2</sup>C-Register REG19 (LIMERIC control, Taste)

| Bit | Name  | Function                                            |  |

|-----|-------|-----------------------------------------------------|--|

| 07  | TASTE | direct LIMERIC register access, SNERT address F3hex |  |

# Application Note AN97017

#### TABLE 23 I<sup>2</sup>C-Register REG20 (LIMERIC control, Status)

| Bit | Name   | Function                                            |  |

|-----|--------|-----------------------------------------------------|--|

| 07  | STATUS | direct LIMERIC register access, SNERT address F4hex |  |

#### TABLE 24 I<sup>2</sup>C-Register REG21 (LIMERIC control, Wanted Value)

| Bit | Name | Function                                            |

|-----|------|-----------------------------------------------------|

| 07  | WVAL | direct LIMERIC register access, SNERT address F5hex |

#### TABLE 25 I<sup>2</sup>C-Register REG22 (LIMERIC control, Noise Estimator)

| Bit | Name       | Function                                            |  |

|-----|------------|-----------------------------------------------------|--|

| 07  | NOISE EST. | direct LIMERIC register access, SNERT address FAhex |  |

#### 5.2.2 Acknowledgement of bytes

The IPQ  $\mu$ C acknowledges always the 22 register bytes (maximum number) independent from their contents. If the master  $\mu$ C transmits more than 22 register bytes, the slave  $\mu$ C will not acknowledge the following bytes.

# Application Note AN97017

#### 5.3 Receiving status information from the IPQ μC

The IPQ  $\mu C$  is able to transmit one status byte and the 2 motion sum registers to the main  $\mu C$ . The IPQ  $\mu C$  then works as a slave transmitter.

#### 5.3.1 I<sup>2</sup>C transmission protocol

The I<sup>2</sup>C bus transmission protocol for transmitting the status byte has the following format:

| S | Start | Slave address 69H | Ack | Status | Ack | motion | Ack | motion | NAck | Stop |

|---|-------|-------------------|-----|--------|-----|--------|-----|--------|------|------|

|   |       |                   |     | byte   |     | sum A  |     | sum B  |      |      |

#### 5.3.2 Contents of status byte

The status byte contains the following information:

TABLE 26 Readregister 1, Statusregister

| Bit | Name             | Function                                                                                                                                    |

|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | NON_IL           | Source with interlaced picture     non-interlaced source detected via software                                                              |

| 1   | SF_DONE          | 0: SCREEN FADE is active 1: SCREEN FADE is done                                                                                             |

| 2   | LFR_PHASE        | 0: LFR_PHASE=0<br>1: LFR_PHASE=1                                                                                                            |

| 3   | MOVIE_FLAG       | 0: no movie source detected 1: movie source detected                                                                                        |

| 4   | MOVIE_PHASE_FLAG | the MOVIE_PHASE_FLAG information is only relevant if MOVIE is set; 0: normal movie phase relation (ABAB) 1: shifted movie processing (BCBC) |

| 5   | PORT24           | bit setting read from port bit P2.4 0: P2.4=0 1: P2.4=1                                                                                     |

| 6   | READY            | 0: not ready to accept IIC commands 1: ready to accept IIC commands                                                                         |

| 7   | WATCH            | Watchdog bit; will be toggled when status byte is read by master $\mu C,$ initialized with 0                                                |

### Application Note AN97017

#### TABLE 27 Readregister 2, (PROZONIC MPD MSByte A)

| Bit | Name         | Function                                                                                   |

|-----|--------------|--------------------------------------------------------------------------------------------|

| 07  | MOTION_SUM_A | MSByte of PROZONIC read register for SAD of luminance values per field, result for field A |

#### TABLE 28 Readregister 3, (PROZONIC MPD MSByte B)

| Bit | Name         | Function                                                                                   |

|-----|--------------|--------------------------------------------------------------------------------------------|

| 07  | MOTION_SUM_B | MSByte of PROZONIC read register for SAD of luminance values per field, result for field B |

The ready bit in the first byte will be cleared after the IPQ  $\mu$ C has received I<sup>2</sup>C register bytes. It will be set again after the evaluation of all bytes is completed and an external interrupt (VDFL from ECO4) initiating data transfer from IPQ  $\mu$ C to ECO4, PANIC, PROZONIC is not currently serviced.

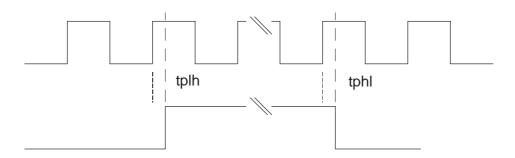

#### 5.4 Timing aspects

The maximum allowed response time between accepting register bytes and the execution of the commands handled by the IPQ  $\mu$ C is 90 ms. This time is only relevant when field memory control modes are changed. Field memory control modes are: Movie, Sat, LFR, Still, Multi-PIP mode. When a field memory control mode has been activated, the IPQ  $\mu$ C waits max. 40 ms until a new frame starts in LFR mode (4 x 100Hz field repetition time). Then it takes another 40 ms until one new frame has been completely transmitted in order to run the new mode.

The maximum allowed total clock stretch time of the IPQ  $\mu C$  within one I<sup>2</sup>C message is 5 ms.

The minimum wait time between sending two I<sup>2</sup>C bus register data packages varies from 12 ms (no field memory control modes have changed) to 90 ms (field memory control modes have changed).

If the user wants to make sure that a complete I<sup>2</sup>C bus register data package is transmitted without being interrupted by VDFL IRQ  $\mu$ C routine and the slave  $\mu$ C is free for I<sup>2</sup>C after the master  $\mu$ C transmits I<sup>2</sup>C data, the I<sup>2</sup>C data package should be transmitted between 3 and 5 ms after VDFL occurred. The slave  $\mu$ C sets bit 6 of the status byte when it is ready to accept I<sup>2</sup>C commands.

#### Multi-PIP:

The time between two I<sup>2</sup>C bus commands activating 2 different PIP picture positions should not be smaller than 120 ms.

#### Screen fade:

As long as this mode is active (86 fields = 860 ms in normal mode), all other mode changes are ignored.

# Application Note AN97017

#### 6. Functional description

The functional description includes the description of all features of the IPQ module which can be controlled over the I²C-bus interface.

The evaluation of I<sup>2</sup>C bus register data is done with respect to a certain priority structure. The priotrity structure of the field memory control modes are shown in Fig. 6. In the following sections certain restrictions on bit settings in the I<sup>2</sup>C register bytes which limit the possibilities of combining field memory control modes (Movie, Sat, LFR, Still, Multi-PIP mode, Progressive Scan) and/or secondary control commands are listed (see chapter 5.2).

#### 6.1 Field memory control modes

#### 6.1.1 LFR mode

Software Control: IIC-Register 1, Bit 5 (LFR)=1

The Line Flicker Reduction Mode is the default control mode. It is activated if the control bit LFR is set. In this display mode the sequence of the four 100 Hz fields per input frame is built as follows:

The first field is the original field A. The second field is a median filtered field A\*. The median filter uses two lines from field A and the line in between from field B as input information. The third output field B\* is again median filtered. The inputs are derived from two lines taken from field B and the line in between from field A. The last field is the original field B.

Control mode: AA\*B\*B (ABAB display raster)

Restrictions: The LFR mode cannot be combined with:

MPIP (Multi-PIP)

GENERATOR Mode

Disabled modes: AABB mode, forced MOVIE mode Combination exclusions secondary control modes: none

#### 6.1.2 AABB mode

Software Control: IIC-Register 1 = 0H

This mode is the field memory control mode which is active if no field mode control bits have been set (lowest priority). It is the most simple 100 Hz conversion mode. Only the first field memory is necessary for the field doubling. For low cost concepts it is possible to leave out the PROZONIC. The software control supports both hardware configurations with or without PROZONIC (VRE1 control).

Control mode: AABB (AABB display raster)

Restrictions: The AABB mode cannot be combined with:

MPIP (Multi-PIP)

GENERATOR Mode

Disabled modes: none

Combination exclusions secondary control modes: none

# Application Note AN97017

#### 6.1.3 Movie mode

Software Control: IIC-Register 1, Bit 6 (MOVIE)

The MOVIE mode is foreseen for a movie source where the time resolution is only 25/30 Hz. In this case the median filter of PROZONIC can be switched off and a simple ABAB display is shown (frame repetition). The sequence of the video fields (odd/even) is not defined in relation to the movie pictures. So the IPQ  $\mu$ C has to find out whether a movie transmission takes place and in which phase relation it is transmitted. A forced activation of the MOVIE mode in case of a video source transmission would cause severe movement effects.

Control mode: ABAB, display raster ABAB

Activation/restrictions: It is activated if the MOVIE bit is set and the bit AUTO\_MOVIE is cleared (forced MOVIE mode). In case AUTO\_MOVIE is set the mode is only active if the software routine has detected a movie source (automatic movie detection routine). The result of the movie detection is copied to the status byte.

MOVIE mode does not run in the Multi-PIP mode.

Disabled modes: AABB mode

Combination exclusions secondary control modes: none

#### 6.1.4 Phase adaption for the movie processing

Software Control: IIC-Register 1, Bit 7 (MOVIE\_ PHASE)

The Phase bit can be set in combination with the bit MOVIE. It determines the phase relation for the frame repetition in relation to the incoming fields. The converter performs an ABAB conversion if MOVIE\_PHASE is cleared and a BCBC conversion if MOVIE\_PHASE is set.

The forced movie mode can be used in case of a PALplus transmission where the information whether a movie is transmitted or not can be derived from a special information line.

Control mode: ABAB for MOVIE\_PHASE = 0, BCBC for MOVIE\_PHASE = 1 raster (field phase is shifted).

Activation/restrictions: It is activated if the MOVIE\_PHASE bit is set. If the bit is cleared the display raster is the normal ABAB.

Combination exclusions secondary control modes: none

#### 6.1.5 Automatic movie mode detection

Software Control: IIC-Register 1, Bit 4 (AUTO\_MOVIE)

In the automatic movie mode (AUTO\_MOVIE=1) the phase information is generated by the software internally and the control bit MOVIE\_PHASE has no influence. Via the status register the phase information can be read. It is coded in the bit PHASE\_Flag.

The bit AUTO\_MOVIE activates the software routine to detect whether a video or movie source has to be 100 Hz converted. Furthermore the phase relation between video (odd/even) and movie picture has to be calculated.

Activation/restrictions: It is activated if the AUTO\_MOVIE bit is set.

The movie detection is based on measurements of absolute luminance differences between successive input fields, pixel by pixel. These differences are summed over the whole active field and deliver a result every field which can be read by the  $\mu$ -controller. In case of a film source with sufficient movement, the measurement results will alter from field to field between high and low values. The microprocessor filters this data (low pass loops) and generates the movie and phase information.

Combination exclusions secondary control modes: none

# Application Note AN97017

#### 6.1.6 Automatic LFR phase adaptation

Software Control: IIC-Register 5, Bit 6 (ENA\_LFR\_PHASE)

If a movie source is 100 Hz converted in the LFR mode (median based field interpolation) the motion effects in e.g. vertically scrolling text information can be reduced, if the LFR sequence AA\*B\*B is controlled with the correct phase relation to the original movie picture.

Activation/restrictions: If the bit ENA\_LFR\_PHASE is set a phase adaptation of the LFR sequence for movie sources is performed. If the bit is cleared, the LFR sequence is fixed according the field recognition of the memory controller.

The movie detection in this mode works similar to the automatic movie detection. The only difference is that the processing times implemented in the software are longer, because the movie detection does not have to decide very quickly.

There is no need to switch between MOVIE and LFR mode. The LFR mode is activated always, only the phase relation of the LFR sequence towards the video fields (even / odd) is changed if necessary.

Combination exclusions secondary control modes: none

#### 6.1.7 Generator mode

Software Control: IIC-Register 1, Bit 1 (GENERATOR\_MODE)

The bit GENERATOR\_MODE activates a stable 100 Hz display with a fixed field length of 312.5 lines. The display field length is not adapted to the video source. If additionally the 27 MHz PLL is unlocked via the control bit PLLMID the display is also in a horizontally free running mode. The conversion mode is reduced to a four times single field repetition (AAAA) in this unsychronized mode. This special mode can be used to get a stable OSD picture without a source or with a very noisy source. It does also improve the picture stability for a tuner channel search.

#### 6.1.8 Satellite mode

Software Control: IIC-Register 1, Bit 2 (SAT)

In the satellite mode all the four 100 Hz display fields are derived from the output of the median filter. The median filter filters out details occurring in only one line. This fact can be used to suppress typical FM noise dropouts which normally occur uncorrelated in the field. A bad satellite signal reception can be improved quite effectively in this mode without deteriorating the picture quality.

Control mode: A\*A\*B\*B\* (display raster AABB)

Activation/restrictions: Satellite mode is activated if the SAT bit is set. LFR, CINE mode or AABB display raster doesn't run in Satellite mode.

#### 6.1.9 Progressive Scan Mode

Software Control: IIC-Register 1, Bit 0 (PSC)

Control mode: 50/60 Hz, 1250/1050 lines (display raster: non-interlaced)

If the bit PSC is set a progressive scan mode is activated. The de-interlacing function (line interpolation) is performed with the help of the PROZONIC median filter. This mode could be preferably used for NTSC sources. The number of lines per field (525 lines / 60 Hz) is doubled and additionally the line flicker is removed. For NTSC

# Application Note AN97017

sources a reduction of the visibility of the line structure is more important than the reduction of large area flicker (60/120 Hz) because a 60 Hz display shows much less large area flicker than a 50 Hz display.

Activation/restrictions: It is activated if the PSC bit is set.

Disabled modes: - Movie mode

- LFR mode- AABB mode

Combination exclusions secondary control modes: none

#### 6.1.10 Multi-PIP

Software Control: IIC-Register 4, Bit 6 (MPIP)

The Multi-PIP feature uses the field memories of the 100 Hz converter to generate or to support a Multi-PIP display. This function can be used for channel overview or photo-finish. Photo-finish shows a sequence of frozen pictures of one source stored with constant time steps. If the PANIC is implemented in the 100 Hz module an external PIP module is necessary. The PIP display is assumed to be positioned at the bottom right of the screen. The PIP information is written to the desired MPIP position in the memory.

If no PANIC is implemented there are two possibilities to implement the MPIP function. The first possibility is described above. For low cost concepts the internal MPIP function of the memory controller SAA 4952 can be used alternatively. In this case no external PIP-Module is required. The PIP pictures however are generated without appropriate filtering and show aliasing effects if the input pictures have a lot of details.

#### Function:

Multi picture-in-picture active for MPIP = 1, 3x3 MPIP for NPIP=0; 4x3 for NPIP=1 (external PIP) or 4x4 for NPIP=1 (internal PIP processing)

The positions are chosen via the bits POS0 to POS3

Combination exclusions secondary control modes: not combinable

#### 6.1.11 Still picture

Software Control: IIC-Register 2, Bit 3 (STP)

It is possible to activate a still picture function in every control mode of the scan converter. The processing of this option is adapted to the conversion mode being activated before.

Control mode: a) AA\*AA\* (full frame median filtered)

b) AAAA (single field control)

c) ABAB

d) PSC (frame based still picture)

The display raster in still picture is always ABAB.

Activation/restrictions: It is activated if the STP bit is set.

Disabled modes: none

Combination exclusions secondary control modes: none

Detail information:

# Application Note AN97017

If Still picture is performed while Noise reduction is active, a noise reduced frozen picture will be displayed.

Still picture mode at the different display modes:

Normal mode (AABB) Still Picture mode => AAAA

LFR mode (AA\*B\*B) Still Picture mode => AA\*AA\*

MOVIE mode(ABAB) Still Picture mode => ABAB

SAT mode (A\*A\*B\*B\*) Still Picture mode => A\*A\*A\*

#### 6.1.12 Vertical Zoom Function

Software Control: IIC-Register 3, Bits 0 to 2 (VZOOM\_0 to VZOOM\_2)

Activation: It is activated if the VZOOM bit is set. The bits VZOOM\_0 to VZOOM\_2 determine the zoom factor according to the  $I^2C$  register table of REG3.

Four different vertical zoom modes are implemented. These zoom factors are 1.1, 1.27, 1.33, 1.5 and 2.0.

The vertical sample rate conversion of PROZONIC can cope with the various letterbox formats. The sample rate conversion is performed on adjacent lines of a frame, the frame information consists of original and median filtered lines. This feature is used to display sources with e.g. 16:9 or 14:9 aspect ratios on 4:3 displays without side panels.

#### 6.2 Secondary control commands

#### 6.2.1 General

Secondary control commands are:

(\*: all combinable)

- Frequency selection/picture position

- Acquisition field frequency (\*)

- Noise reduction

- Split screen

- Screen fade

- Peaking (\*)

- CTI

- Port settings

- Initialization command

- HWE1 fine delay setup control (\*)

- VWE1 delay setup control (\*)

# Application Note AN97017

#### 6.2.2 Frequency selection (only on modules without SAA 4995, PANIC)

Software Control: IIC-Register 3, Bit 4 to 7 (FSA0, FSA1 and FSD0, FSD1)

Function: Selection of the horizontal conversion mode (horizontal compression or zoom factor)

The following frequency combinations will be accepted by the IPQ µC:

| acquisition<br>frequency<br>[MHz] | display<br>frequency<br>[MHz] | mode     | compression/<br>zoom factor<br>[%] |

|-----------------------------------|-------------------------------|----------|------------------------------------|

| 12                                | 32                            | compress | 33                                 |

| 13.5                              | 27                            | normal   | -                                  |

| 13.5                              | 32                            | compress | 19                                 |

| 13.5                              | 36                            | compress | 33                                 |

| 16                                | 27                            | zoom     | 19                                 |

| 16                                | 32                            | normal   | -                                  |